展会名称:2024南昌国际半导体光电技术与显示应用博览会

首届南昌国际半导体光电产业高质量发展论坛

时间:2024年9月27-29日

地点:南昌绿地国际博览中心

展馆详细地址:南昌市红谷难区怀玉山大道1315号

NAND发展似乎进入了一个怪圈。

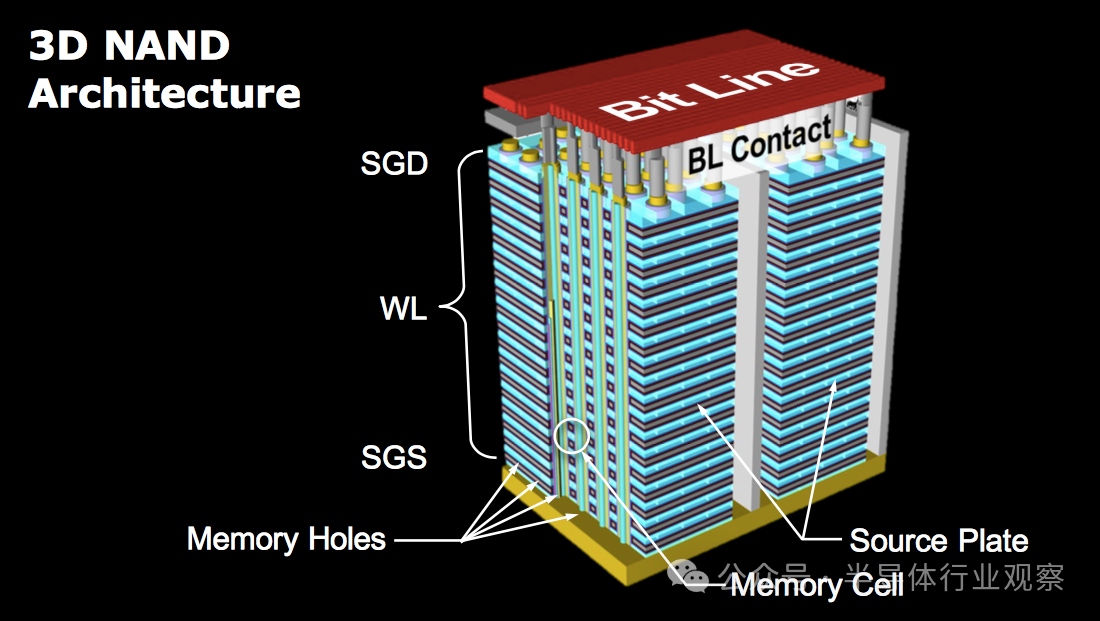

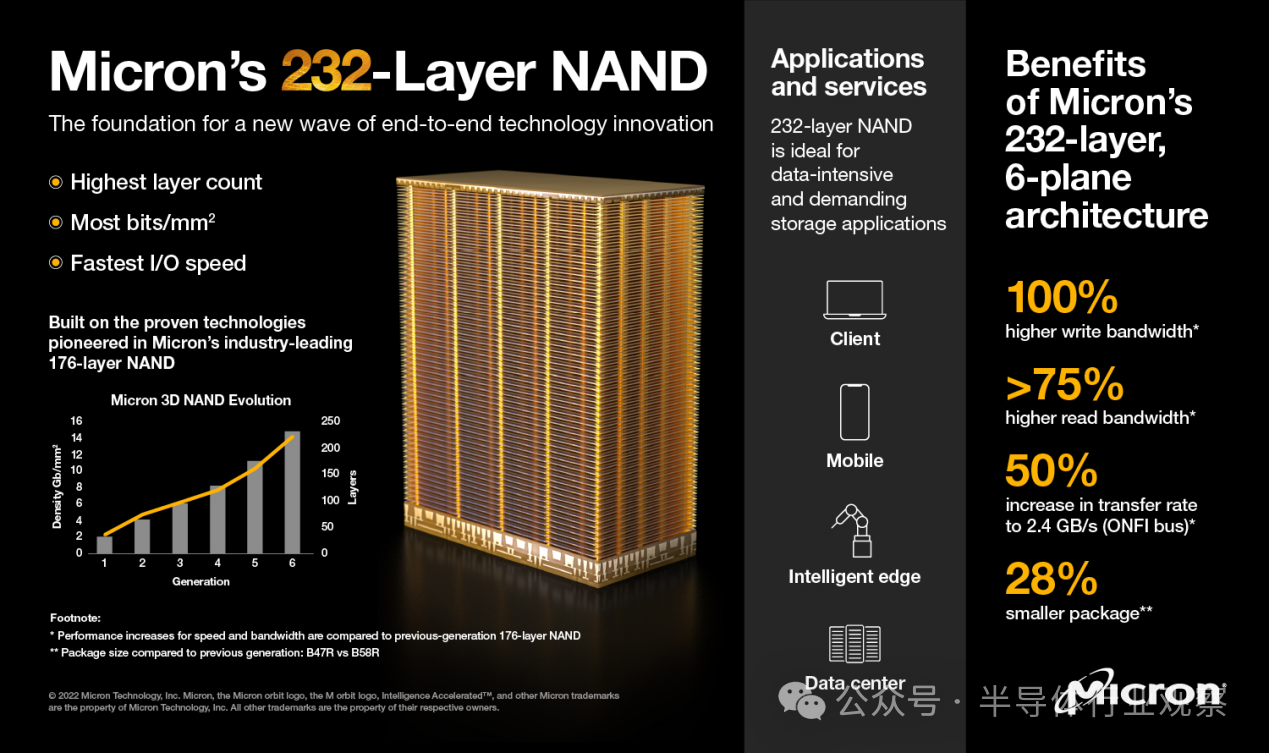

曾经的东芝存储,如今的铠侠刚宣布了一个好消息:随着存储市场的复苏,铠侠已经结束了NAND 闪存的减产策略,目前铠侠在日本三重县四日市和岩手县北上市两座工厂产线的产能利用率已提升至100%。 此外铠侠在连续 6 个季度的亏损后也在上季度重新实现了103亿日元盈利,由三家银行组成的贷款银团同意对铠侠即将到期的5400亿日元(当前约249.25 元人民币)贷款进行再融资,并提供2100亿日元的新信贷额度。 而其他存储厂商,也在努力恢复之前削减的NAND产能,三星的 NAND 闪存产能已攀升至 70% 左右, SK 海力士正在加大高容量 NAND 产品(如高容量 eSSD)的生产,而西部数据则正将其生产利用率提高到 90% 左右。 不过,NAND市场的寒冬恐怕还未结束,有专家担心,产量的快速增长可能会超过需求,从而抑制 NAND 闪存价格的上涨,韩国工业经济贸易研究院研究员金仰N鹏表示:“除了人工智能数据中心使用的高容量 NAND,很难说整个 NAND 市场都在复苏,产量的突然激增可能会压低一直在上涨的 NAND 价格。” 这也意味着,接下来的一年中,NAND市场依旧存在着许多不确定性,能否像DRAM一样快速恢复元气,还是一个未知数。 而更大的挑战仍然是技术层面的,3D NAND的下一步到底是什么? NAND,何去何从 对于NAND来说,21世纪的头十年和DRAM别无二致,借助不断发展的摩尔定律,通过更高分辨率的光刻,持续微缩晶体管,从而带来存储密度和性能的提升。 但在2010年之后,这条微缩之路逐渐走到了尽头,一方面,EUV技术量产比想象中更慢,DUV已经达到了极限,而曲线救国的多重曝光方法带来的高成本与低良率也是NAND厂商所不能接受的。 最终,3D NAND技术成为了新的发展方向,传统NAND Flash 采用平面设计,而3D NAND 是以则由原本平铺的存储单元所堆叠而成,由传统单层存储提升至高达上百层的堆叠,让其存储容量相较于传统2D NAND Flash有了大幅提升。 直到今天,3D NAND也在持续推动着整个存储市场的发展,但行业内的对NAND未来发展方向的争议却似乎从未停止过。 早在2004年国际固态电路会议(ISSCC)上,Sub-Micron Circuits的Jagdish Pathak就表示:“为了在2010年之后继续缩放闪存技术,需要进行深入研究。90纳米的闪存已经投入生产,在65纳米上存在争议,有些人认为可以继续缩放,有些人则表示怀疑。我认为在接近45纳米时,浮动栅极结构会面临更大的缩放困难。有很多很多的挑战。” 三星存储部门副总裁Kim Ki-Nam博士选择了基于硫属化物的方法(即PCRAM、PRAM和Ovonics统一存储器),这种方法依赖材料的相变效应来实现切换。Kim说:“它比其他方法具有更好的可扩展性。” 日立中央研究实验室的Tomoyuki Ishii正在研究NanoCrystal存储技术,这是一种单电子存储技术的衍生方法。Ishii说:“它可以垂直和水平缩放,多状态数据提供了所有替代方案中最低的每比特成本。氧化物可以缩放到5纳米的厚度,而且这也是一个纯硅工艺。”NanoCrystal的挑战是编程和擦除时间慢以及高电压。Ishii认为这些问题将在两到三年内解决。 英飞凌科技和摩托罗拉则把资金投入到MRAM上。英飞凌的Sitaram Arkalgud称MRAM是“对通用存储应用极具吸引力的候选者”。然而,Jagdish Pathak指出,第一篇关于MRAM的论文发表在1991年,但至今仍没有商业产品。 英特尔闪存开发总监Greg Atwood说:“目前尚不清楚是否存在或即将出现能够挑战浮动栅极的技术。” 可以看到,20年前,各家对NAND的下一步提出了不同看法,最终,NAND 闪存行业放弃了传统的扩展方式。首批商用 3D NAND 产品于 2013 年推出,堆栈数量为 24 个字线层 (128 Gb)。根据供应商的不同,结构存在差异,以不同的名称为人所知,例如 V-NAND 和 BICS,3D NAND成为了第一个也是唯一一个将真正的 3D 产品推向市场的技术。 为了保证NAND密度能够不断提升,厂商们在这20年时间中实施了更多创新,从而促进具有挑战性的 3D 工艺或进一步提高位密度,后者的一个例子是将每个单元的比特数增加到最多4个,这是NAND闪存技术的真正优势。例如,使用4个比特时,多级单元在每个单独的晶体管中使用16个离散电荷级别,这得益于足够大的存储窗口。 另一个显著的创新是用电荷陷阱单元取代了浮栅单元,这涉及更简化的工艺流程。这两种单元类型的工作原理相对类似,但在电荷陷阱单元中,捕获层是绝缘体——通常是氮化硅——这减少了邻近单元之间的静电干扰。现在,大多数3D-NAND结构都以这种电荷陷阱单元为基础。 值得一提的是,3D NAND依旧在不断的堆叠当中,其中几家主要的NAND厂商,目前已经向200层以上发起进攻。 三星一直处于3D NAND创新的前沿。他们在V7中采用了双层结构,并引入了COP整合以提高性能。随着V8 236层1 Tb TLC产品的发布,三星展示了其不断突破技术界限的承诺。展望未来,三星已经在计划V9,采用280层COP V-NAND和类似于其他领先竞争对手的混合键合技术。 铠侠(KIOXIA)和西部数据(WDC)保持了BiCS结构,专注于提高层数。通过宣布第八代BiCS产品具有218层,并计划推出具备284层的后续版本,铠侠展示了其在NAND技术进步方面的决心。 美光(Micron)转向CTF CuA整合,凭借 176L 和 232L 产品的发布引领市场。他们还在开发 Gen7,可能会跳过 300 层节点,瞄准 400 层设备,展现出他们对未来创新的雄心。 SK海力士继续使用4D PUC结构,计划大规模生产238层V8 4D PUC产品,其正在为进一步发展做好准备,可能在不久的将来达到370层或380层。 长江存储(YMTC)的Xtacking结构取得了显著进展,从176层跳到232层。尽管面临芯片禁令带来的挑战,其仍然专注于开发更先进的QLC设备和multi-Xtacking技术。 旺宏电子(MXIC)以其第一代3D NAND芯片进入市场,应用于任天堂Switch等产品。计划推出具有96层的第二代产品,其准备在行业中取得进一步进展。 厂商们甚至已经开始绘制1000层的蓝图。激进的铠侠近期表示,以每年 1.33 倍的增长率,3D NAND到 2027 年将可达到 1,000 层的水平,三星则在之前预测,到 2030 年左右,其 3D NAND 可以堆叠超过 1,000 层。 随着 3D NAND 的成熟,SLC 和 MLC 逐渐被淘汰,TLC 占据主导地位,而最新的QLC 比 TLC 密度更高,而且还有五级单元工作,成本较低。但问题也接踵而至,尽管 QLC SSD 密度高且成本较低,但性能并不好,更容易出错,使用寿命也不如更昂贵的 TLC NAND 的 SSD 长。 此外,尽管 NAND 取得了诸多进步,但它本身能做的事情非常有限,主要在于其写入速度仍会阻碍其大幅缩小与 DRAM 的差距或达到 Optane 的性能,这主要归结于量子力学,这意味着闪存写入速度为数十毫秒,而 DRAM 写入速度为数十纳秒,该限制将使 NAND 闪存无法填补空白。 AI会是希望吗? AI不仅带动了DRAM市场中HBM部分的增长,也给NAND带来了一些好消息。 根据市场研究公司Omdia在6月10日的报告,预计今年QLC NAND市场规模将比去年增长85%,其在整体NAND市场的份额将从去年的12.9%增加近8个百分点,达到今年的20.7%。 Omdia预测,到2027年,QLC NAND将在整个NAND市场中占据46.4%的份额,三年内份额将翻倍,接近目前占据51%市场份额的三级存储单元(TLC)产品。值得注意的是,尽管直到去年QLC NAND产品主要面向消费者,但今年需求预计主要增长在更高价位的服务器产品上。 QLC NAND的特性与大型科技公司在其服务器上部署生成性AI的需求非常契合。SSD比传统硬盘驱动器(HDD)提供更快的数据读写速度,这突显了每单位面积存储更多信息和减少功耗的优势。NAND制造商也在迅速响应对QLC NAND需求的激增。有乐观的说法认为,NAND市场的“春天”可能比预期的更强劲。像去年基于AI需求的HBM需求增长一样,NAND市场可能会经历类似的长期市场形成。 不过,尽管QLC NAND吃到了AI的红利,但它本身的问题依旧存在,尤其是在高读取工作负载的环境下,不论是寿命还是性能,都会受到很大的影响。 有趣的是,AI在带动NAND市场发展的同时,也给NAND提供了一种解题思路。 在使用 AI 来更好地管理 SSD 中的 NAND这方面,主控厂商已经走在了前面,据报道,Microchip Technology 的闪存控制器内嵌有机器学习引擎,以帮助延长 NAND 的寿命并改善比特错误率。 在一次独家采访中,Microchip 数据中心解决方案业务部门的 Ranya Daas 说,虽然在后台使用算法会增加开销,因为它需要处理能力,但她表示,机器学习可以使 NAND 单元训练以减少读取和重试次数,从而优化读取电压。“你会从一开始就知道要去读取哪个参考电压。” Daas认为,这种方法有机会延长 NAND 闪存的寿命,减少延迟,并且不增加必须实时进行的后台处理。 此外,SSD 制造商 Phison Electronics 也在利用 AI 来提高闪存在驱动器内的性能。 “你无法克服闪存的固有延迟,” Phison 的首席技术官 Sebastien Jean 在接受 EE Times 独家采访时表示。“它具有自身的延迟结构。在任何现实的工作负载和任何现实的数据量中,你不可能缓存足够的数据以在统计上产生差异。” 除了其第四代 LDPC ECC 引擎外,Phison 还专注于可以通过 AI 改善的痛点,Jean 说。其 Imagin+ 定制和设计服务包括 AI 计算模型和 AI 服务解决方案,以帮助公司客户设计和工程定制闪存部署。 Imagin+ 与 Phison 产品一起工作,优化用于 aiDAPTIV AI+ML 工作负载。aiDAPTIV+ 将 SSD 集成到 AI 计算框架中,以提高 AI 硬件架构的整体操作性能和效率。它结构性地划分大规模 AI 模型,并通过 SSD 卸载支持运行模型参数。Phison 的方法旨在在有限的 GPU 和 DRAM 资源内最大化可执行的 AI 模型。 从某种意义上说,AI 正在使闪存更好地处理 AI。Jean表示,AI 可以用于热/冷映射。在闪存存储阵列采用的早期,公司必须决定哪些数据足够重要以存储在较快的闪存上,而不是较慢的旋转磁盘上。他说,通过改进热/冷检测映射,可以延长驱动器的寿命,减少延迟,并在整个读/写周期内保持更紧密的性能。 在一味强调堆叠的今天,NAND本身的性能寿命遇到了新的挑战,而AI似乎不仅是NAND未来的“衣食父母”,也是它下一步发展的救星之一。 写在最后 对于NAND产业来说,市面上的参与者比DRAM更多,也意味着竞争更加激烈。 当DRAM产业中HBM这样的高附加值产品出现后,也让许多人开始思考,NAND产业的“HBM式变革”在何处,它能否带来产业的新一轮发展。 更高的密度或许可以满足市场目前的需求,但堆叠层数,或许已经不是唯一的答案。 免责声明:来源标记为网络的文章其原创性及文中陈述文字和内容未经我司证实,对本文以及其中全部或者部分内容、文字的真实性、完整性、及时性本站不作任何保证或承诺请读者仅作参考并请自行核实相关内容,版权归原作者所有,如有侵权请联系我们删除。