展会名称:2024南昌国际半导体光电技术与显示应用博览会

首届南昌国际半导体光电产业高质量发展论坛

时间:2024年9月27-29日

地点:南昌绿地国际博览中心

展馆详细地址:南昌市红谷难区怀玉山大道1315号

早前,三星举办了代工论坛。

对于三星来说,举办此类活动的关键在于重新调整行业对该公司竞争力和产能的预期。很难不注意到合作伙伴在为其最新和最出色的 AI 芯片选择竞争对手时,三星希望从 AI 初创公司、汽车客户、智能手机等众多高性能设计中获得支持,并且该公司拥有对电源、高压和 RF 解决方案至关重要的大量传统工艺节点基础。

三星在此次活动中发布的重点是其 SF2Z 工艺节点的路线图。其中,“SF”代表三星代工厂,“2”代表 2nm 级,Z 代表背面供电。SF2Z 将是集成该代 Gate-All-Around 技术(三星称之为 MBCFET)的节点,然后是 BSPDN,以提高性能和能效。

在本文,我们将会深入讨论一些细节,但这里的关键日期是 2027 年——三星预计将在 SF2Z 时进行量产。这将是在该公司量产许多其他 SF2 级节点之后。SF1.4,也就是更早的节点,也将于 2027 年开始风险生产。

三星代工厂:扩张

鉴于《CHIPS法案》资金将流向三星,确定三星设施所在地至关重要。三星的大部分传统和前沿技术都位于韩国,分布在三个城市:

器兴,6号线,65nm-350nm:传感器,电源IC

器兴,S1 线,8nm:智能手机、数据中心、汽车

华城,S3线,3nm-10nm

平泽 S5 线 1 期 + 2 期

平泽S5号线三期建设中

三星在美国也有两个工厂:

奥斯汀(德克萨斯州),S2 线,14nm-65nm:智能手机、数据中心、汽车

泰勒(德克萨斯州),宣布新建 4 座晶圆厂,可容纳 10 座。将包括 SF2、SF4、FDSOI、封装

三星目前的封装设施位于韩国,但同时也拥有全球 OSAT 合作伙伴的巨大影响力。泰勒的扩张计划将成为该公司在韩国境外进行的最大规模扩张,计划为任何美国企业提供现场全面运营,而无需借助亚洲。

制造技术路线图

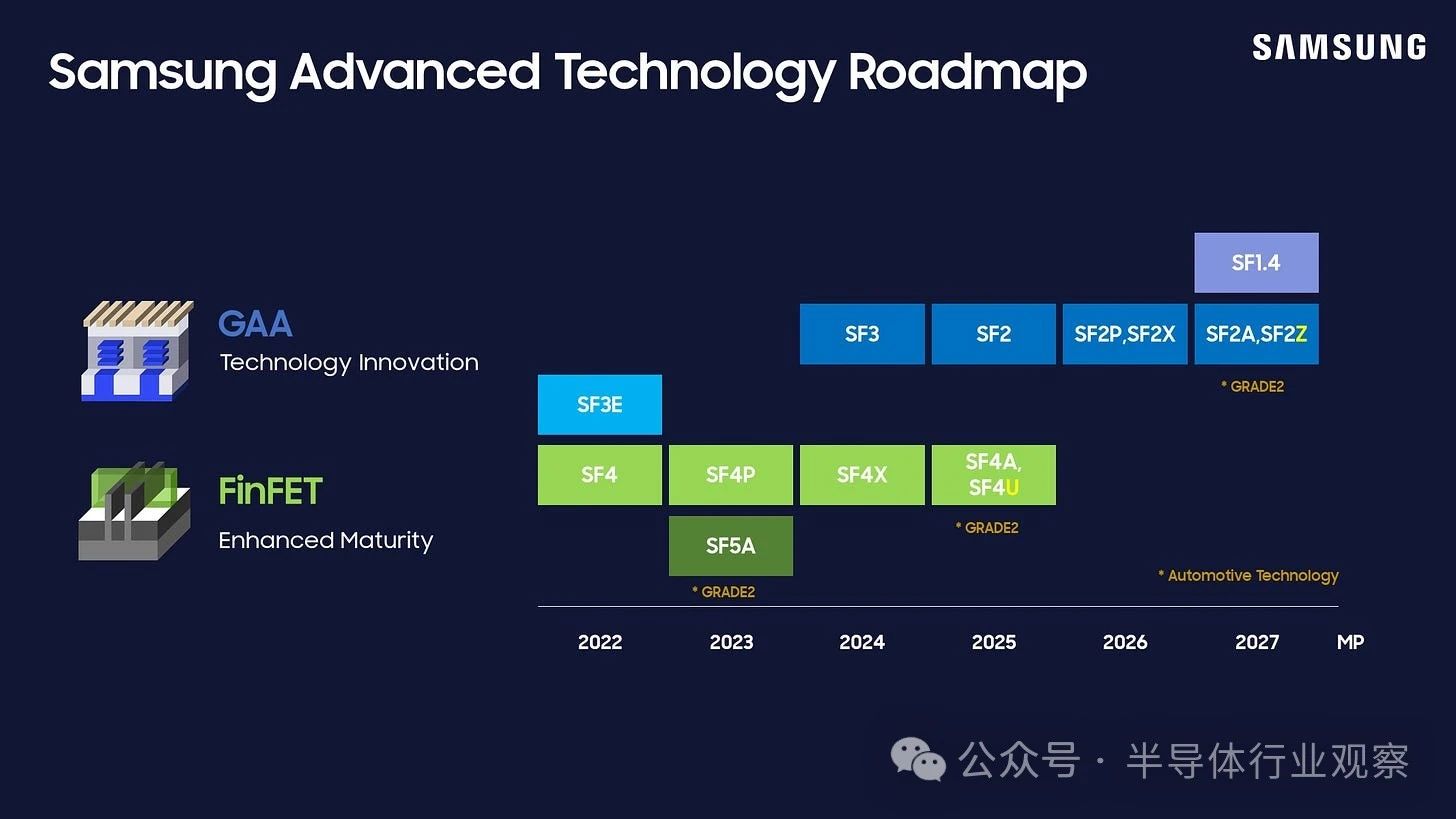

与其他代工厂一样,三星依靠一系列主要的系列工艺节点,从中衍生出许多变体。在这种情况下,主节点是 SF4 和 SF2。

SF4 系列:FinFET

2021:SF4E(E = Early)

2022 年:SF4

2023 年:SF4P(P = Performance, for Smartphone)

2024 年:SF4X(X = Extreme, for HPC/AI)

2025 年:SF4A、SF4U(Automotive, U = Ultr)

三星的 SF4 仍然是 FinFET 节点,事实证明,在智能手机芯片组和大量想要尖端技术的 AI 初创公司中,它非常受欢迎。SF4P 主要针对智能手机领域,泄漏比 SF4 低,而 SF4X 则是大多数 AI 和 HPC 用户最终会选择的产品。对于任何在 2024/2025 年寻找中端 GPU 的人来说,如果它们采用三星制造,那么 SF4X 是您的最佳选择。

由于汽车节点要求更高,三星通常会推出其技术的汽车专用版本,这就是 SF4A 的作用所在。SF4U,虽然被称为 Ultra,但旨在成为 SF4P 的更高价值版本,展示了针对智能手机芯片组制造商的更高端战略,这些制造商希望获得节点改进的好处,但同时又具有略微更大的余量和有效生产。

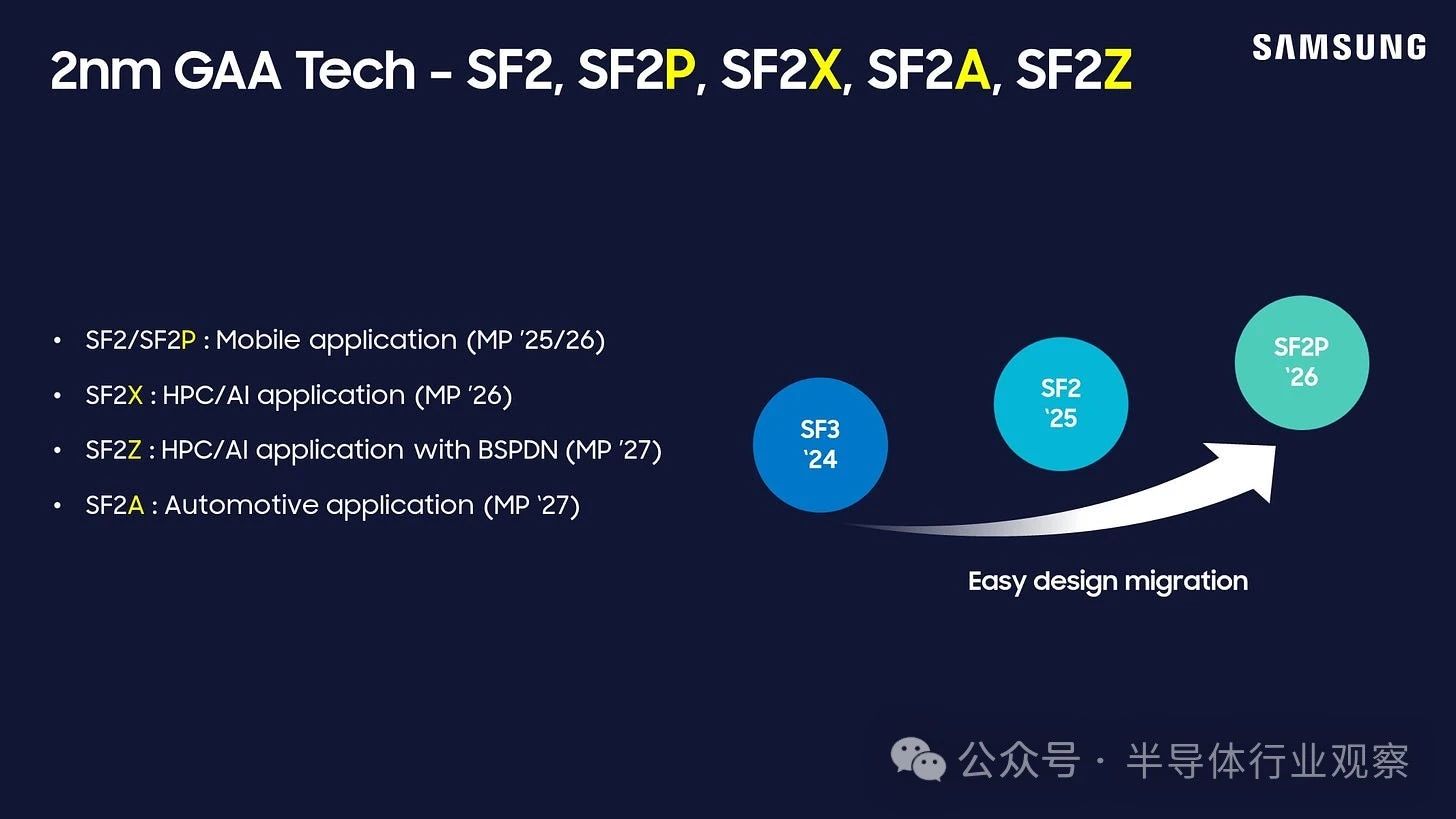

SF2 系列:MCBFET (GAA)

2022 年:SF3E

2024 年:SF3

2025 年:SF2

2026 年:SF2P、SF2X

2027 年:SF2A、SF2Z

所以这可能会有点令人困惑。三星代工厂宣布,它是第一个使用 SF3E 节点生产 GAA 技术的公司——恰当地命名为“early”。据我们所知,虽然自 2022 年以来已投入量产,但它纯粹是一个内部节点,旨在帮助开发该技术。英特尔直到 2025 年的 20A/18A 节点才会推出 GAA,而台积电也在考虑在类似的时间范围内推出 N2。这两家公司都希望迅速将其推向市场,而不是像三星那样提前发布公告。

SF3 是第二代 GAA,已于 2024 年投入量产。这可能会有所回升,但第三代 SF2 将大力向客户推销。关注三星的用户可能会注意到,命名方案中从 SF3 到 SF2 的转变有点奇怪 - 这实际上意味着三星已将其 SF3P 及以后的系列更名为 SF2,可能更符合三星竞争对手使用的命名。争论的焦点一如既往地是竞争对齐,但真正的客户确实知道性能如何,无论节点名称如何。

2026 年,我们将看到智能手机 (SF2P) 和 GAA 的 AI/HPC 变体 (SF2X) 的大规模生产,在这里,我们将非常密切地遵循 SF4 系列的战略。2027 年,我们将获得该汽车变体,但 SF2Z 将 BSPDN 带到了谈判桌上。从活动中的讨论来看,2027 年对于 SF2Z 来说是一个大规模生产日期,而不仅仅是风险生产的理想日期。这意味着 SF2Z 的风险生产将于 2026 年底或 2027 年初开始,首先在韩国,然后在适当的时候转移到美国。

值得注意的是,三星预计 GAA 功率改进的节奏将比 FinFET 更快 - 幻灯片中的一张显示平面晶体管功率(14nm 之前)每年趋势为 0.8 倍,而在 FinFET 期间趋势为 0.85 倍/年。三星预计 GAA 将通过 GAA / MCBFET 将这些改进恢复到每年 0.8 倍。

内存路线图

三星热衷于强调其在内存生态系统中的地位——主要是作为第一大供应商。该公司展示了其自 1992 年以来一直占据 DRAM 第一的位置,目前市场份额为 41%;自 2002 年以来一直占据 NAND 第一的位置,目前市场份额为 32%;自 2006 年以来一直占据 SSD 第一的位置,目前市场份额为 37%。三星将市场视为金字塔。

Tier 1: SRAM

Tier 2: LLC

Tier 3: HBM3E / HBM4

Tier 4: LPDDR6 / LPDDR5X-PIM / LPCAMM

Tier 5: CMM-D (C)

Tier 6: PBSD / CXL-H (C)

我发现这本身就很有趣,因为它展示了三星正在研究的一些即将推出的技术。我们知道内存标准会随着时间的推移而改进,例如从 HBM3 到 HBM4,或者从 LPDDR5 到 LPDDR6,但这里显示三星正在通过其 LPDDR5X 产品线实现内存处理。内存处理是三星多年来一直在谈论的事情,最初专注于 HBM 堆栈,并与 AMD Xilinx FPGA 或定制芯片配置合作使用。它即将出现在 LPDDR5X 的变体上,这一事实意义重大,特别是如果这意味着在中长期内节省电力对 AI 有好处的话。同样在第 4 层上的还有 LPCAMM。最后两个层都是关于内存和存储扩展的,尤其是即将推出的 CXL 标准。

然而,大多数人关注的焦点是 HBM 方面。三星透露了一些数据和时间表:

2022 年:8-Hi 堆栈 HBM3,速度达 900 GB/秒

2024:12-Hi 堆栈 HBM3E,速度为 1178 GB/秒

2026:16-Hi 堆栈 HBM4,速度为 2048 GB/秒

2028年:HBM4E

关于HBM4,三星还透露了很多信息。

芯片密度:24 GB

容量:48GB/cube

数据宽度:2048 位(高于 1024 位)

引脚速度:6 Gbps/引脚(低于 8 Gbps/引脚)

堆叠高度:720 微米(无变化)

键合:铜-铜混合键合(从以前的方法更新)

基本芯片:包括缓冲器、从平面 FET 到 FinFET 的过渡

三星将 HBM4 列为以 70% 的面积和一半的功率提供 200% 的速度。但这并不是故事的结束,因为三星希望定制 HBM 成为最高性能硬件的标准。这意味着包含逻辑和缓冲区的基本芯片将由客户根据其性能配置文件要求进行单独配置。这意味着相同的 HBM4 可以进行读取优化,或支持更多内存加密模式。与更前沿的基本芯片相结合,目标是提取性能并提高效率,这是 AI 人群的两个标志,它们将以无与伦比的方式使用 HBM4。

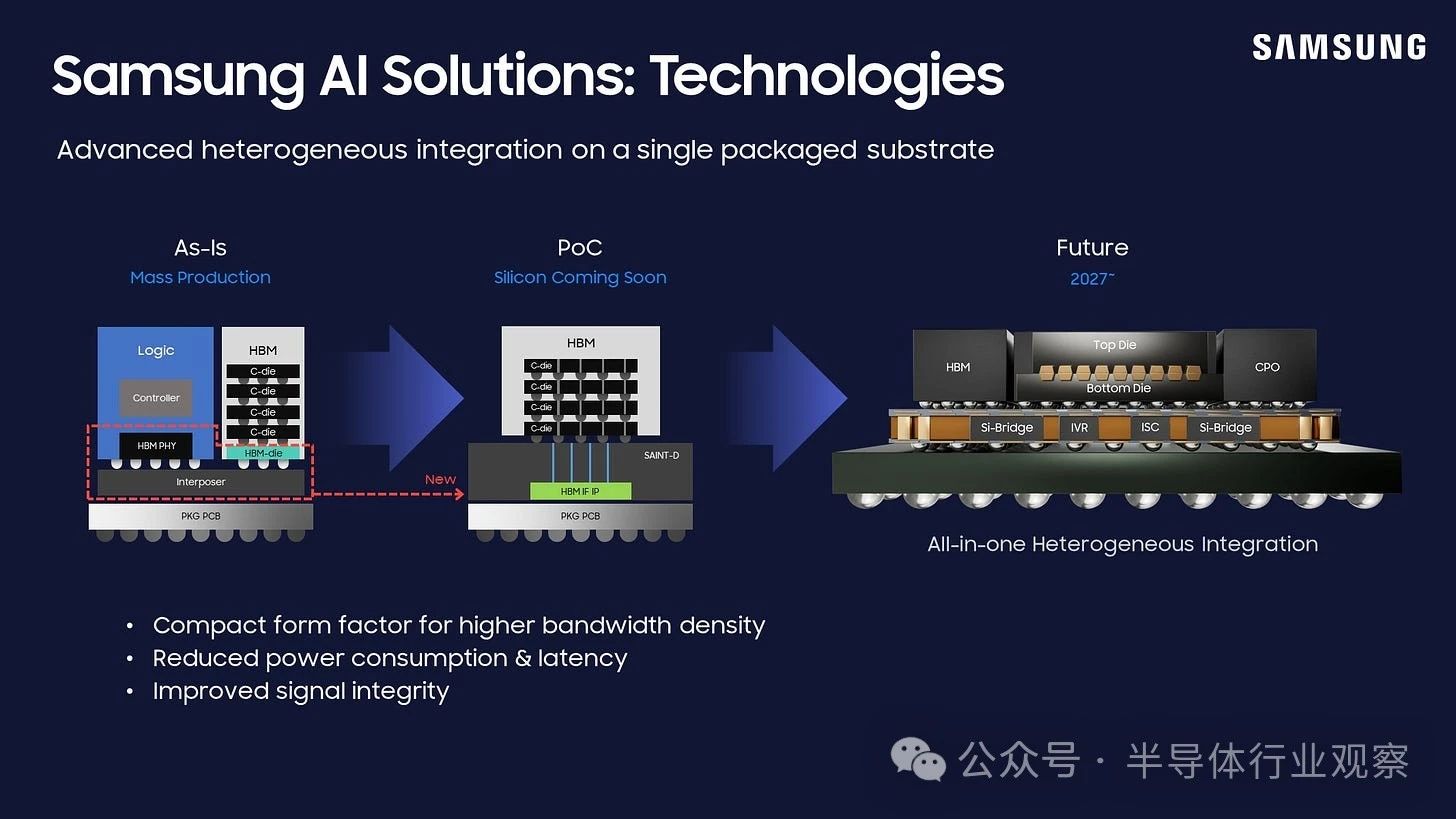

封装

至少从我过去的角度来看,三星一直没有大力推广的领域之一是封装业务。虽然其他代工厂都在推广 CoWoS 和 EMIB/Foveros,但即使没有营销名称来概括,也很难说出三星的封装能力是什么。尽管如此,三星确实参与了先进封装,既用于智能手机,也用于 AI 加速器。

在智能手机领域,路线图如下所示,其中列出了各自的热阻比(thermal resistance ratios):

2016 年:I-POP、1x TR

2018年:FOPLP,TR为0.85倍

2023 年:FOWLOP,0.85 倍 TR

2025 年:FOPKG-SIP,0.65 倍 TR

在人工智能方面,三星制定了以下人工智能芯片的路线图。

目前:2.5D interposer、6 个 HBM3、80 GB 容量、带宽为 3.35 TB/秒

2024:2.5D interposer+、八个 HBM3E、192 GB 容量、带宽为 6.6 TB/秒 2026 年:2.xD 采用 RDL+Si Bridges,8-12 HBM4,576 GB 容量,带宽为 30.7 TB/秒 2027 年:2.xD+3D、逻辑/逻辑和逻辑/内存。16-24 HBM4E,带宽为 70.5 TB/秒 最后一个没有列出容量,但我们谈论的是结合 2.5D 和 3D 功能 - 本质上是将多个 AI 加速器结合在一起。如果基础设计有一个计算芯片和四个 HBM3E 堆栈,这可以被视为类似于 Blackwell。但三星的想法类似于将两个 Blackwell 放在一起。当然没有提到这些 ASIC 的功耗! 在 3D 集成方面,我们确实有一些关于三星何时会提供不同的底部芯片/顶部芯片支持的路线图。 Bottom Die:2025 年推出 SF4X,2027 年推出 SF2P Top Die:2025 年推出 SF2,2027 年推出 SF1.4 这看起来像是计算上的计算的语句,而不是计算上的缓存或缓存上的计算。 三星还提到了共封装光学器件 (CPO:co-packaged optics)。该公司正在投资 CPO 战略,包括电气接口芯片 (EIC:electrical interface chip)、光子接口芯片 (PIC:photonics interface chip) 和用于快速数据传输的光学板。 在演讲之外,我与三星的一位光学工程师进行了交谈,我们讨论了硅波导(waveguides)作为将大量芯片组合在一起的长期解决方案 - 如果您熟悉初创公司 Lightmatter 的 Passage,它可以让多个芯片通过封装通过光相互通信,我们讨论了这是这项技术的潜在未来。今天,大多数 CPO 解决方案都在使用 GlobalFoundries 的 45nm 光子工艺或 imec 200nm 变体 - 因此很高兴看到该领域的竞争。三星表示,他们预计很快就会有 EIC/PIC 概念验证。 最后的想法 路线图表明,三星致力于长期保持领先的地位。成为第一是一回事,但做好又是另一回事。三星拥有强大的本地芯片设计行业——我的名单上至少有六家人工智能初创公司,我知道很多中型人工智能硬件公司都将使用 SF4X,包括 Tenstorrent 和 Groq。 除此之外,确定先进封装市场的走向也是一个额外的好处,我希望看到更多公开讨论和三星能力的例子。论坛是一个良好的开端,我期待看到更多的数据。

免责声明:来源标记为网络的文章其原创性及文中陈述文字和内容未经我司证实,对本文以及其中全部或者部分内容、文字的真实性、完整性、及时性本站不作任何保证或承诺请读者仅作参考并请自行核实相关内容,版权归原作者所有,如有侵权请联系我们删除。